## SI-MONOLITHIC MICROWAVE PRESCALER IC

+ + +

Satoru Watanabe, Satoru Shinozaki, Noboru Kusama,

\* \* \*

Shin-ich Miyazaki and Taka-aki Nakata

+ Microwave and Satellite Communications Division \* 2nd LSI Division

NEC Corporation Yokohama, Japan

### ABSTRACT

This paper describes a Si Monolithic microwave Prescaler IC with a toggle frequency of 3.9 GHz. To optimize circuit parameters and to determine the dominant transistor parameters, precise computer simulation has been used.

An improved IC manufacturing process was developed to achieve the desired parameters and to obtain a transistor cut-off frequency of 10 GHz.

### MICROWAVE PRESCALER IC

In the design of microwave local oscillators for recent digital microwave equipment, automatic phase control technique using a digital frequency divider has been the most suitable solution for frequency stability and analog service channel transmission from the local oscillator(1). A prescaler IC operating in the 1 GHz frequency range is commercially available, but it requires a relatively large 1 GHz VCO and frequency multipliers. A microwave prescaler IC operating in the C-band is a high priority requirement for microwave local oscillator designers.

A typical microwave prescaler consists of a master-slave flip-flop circuit (2). To raise the prescaler toggle frequency, not only improvements in the IC manufacturing process but also circuit parameter optimization is highly desirable.

### COMPUTER-AIDED CIRCUIT DESIGN

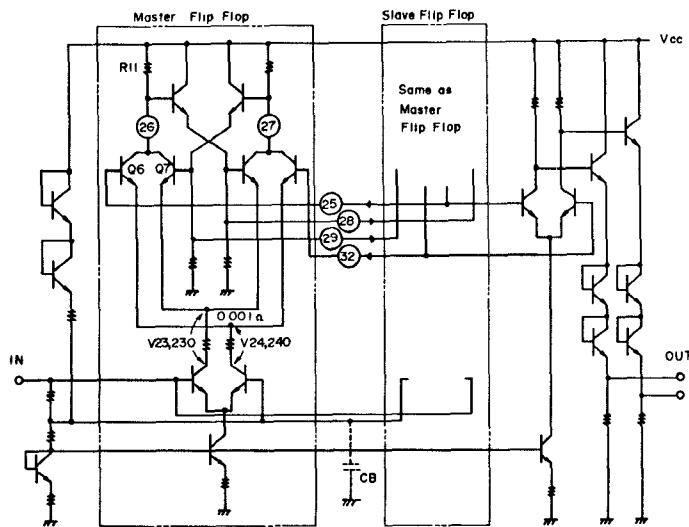

The fundamental circuit of this prescaler consists of a master and slave flip-flop, as shown in Fig. 1.

Prescaler simulation requires a great deal of computing time, for the following reasons:

(A) prescaler simulation relies on transient analysis or iterative calculations, not on frequency response analysis.

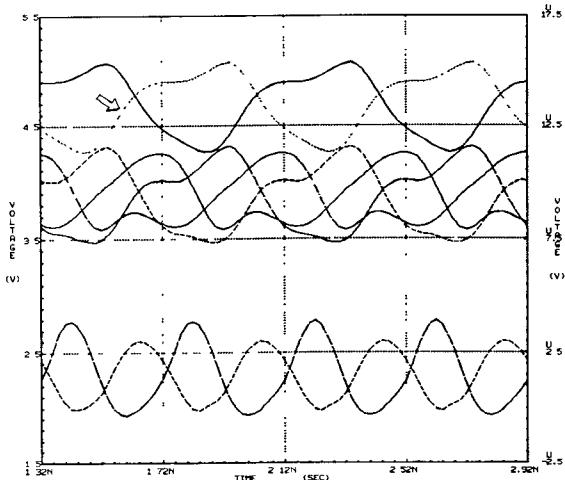

- (B) One pulse analysis is not enough to verify perfect prescaler operation since miscounting occasionally occurs, as shown in Fig. 2.

- (C) Without special initialization, the prescaler can not operate immediately, as shown in Fig. 3.

- (D) One analysis demonstrates only if the prescaler can operate at one particular frequency.

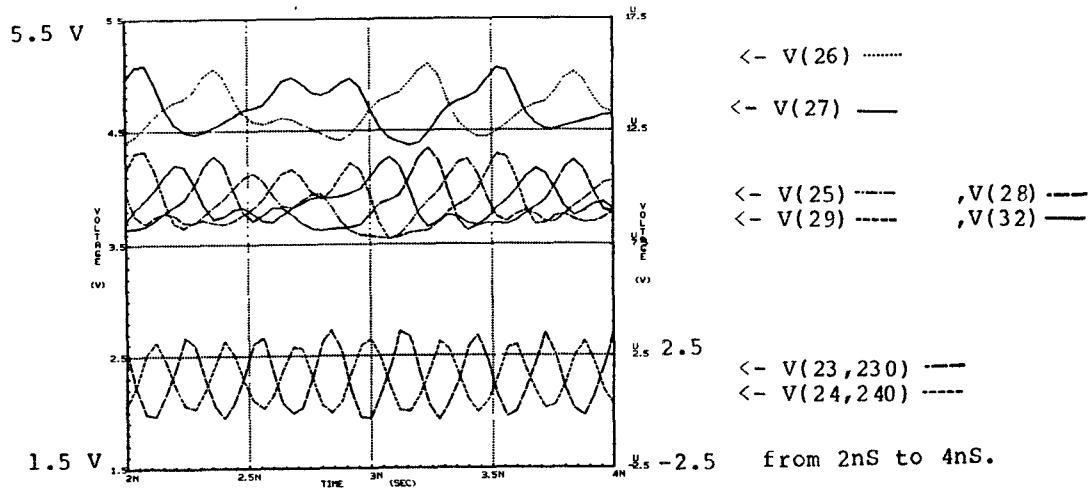

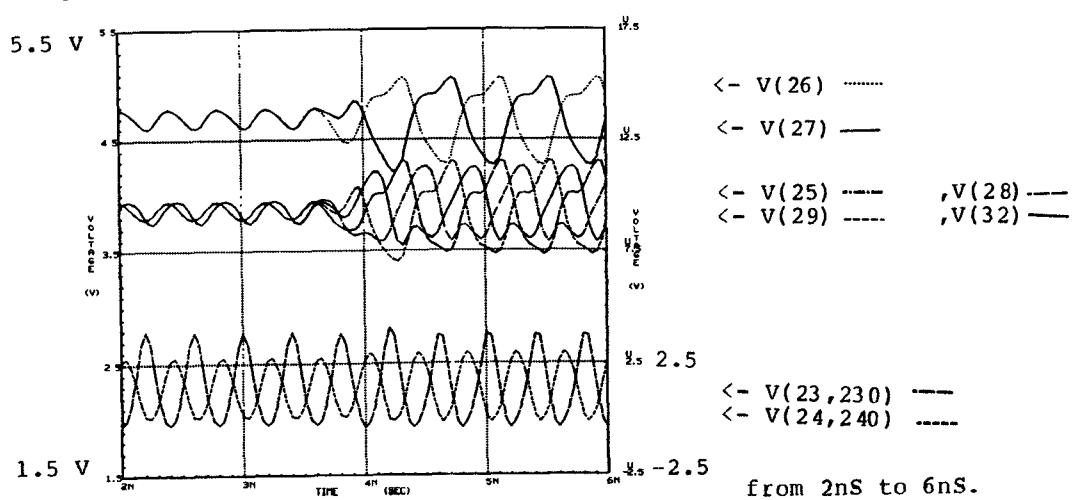

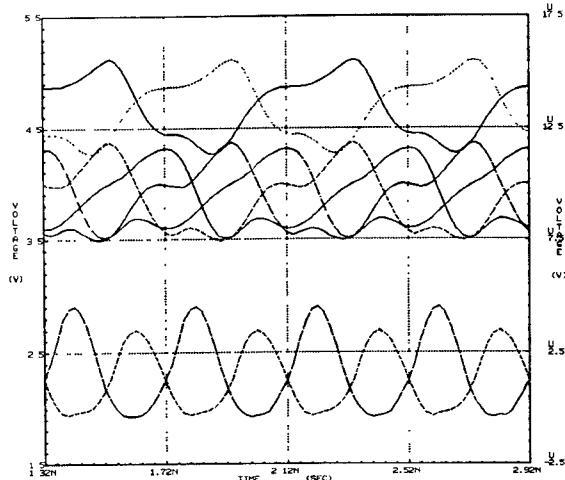

To optimize circuit and transistor parameters much more precisely, pulses at internal nodes are simulated and compared. The master and slave flip-flops are initially set to opposite states using SPICE code ".IC", and the prescaler can operate immediately. A precise wave form can be simulated with this method, as shown in Fig. 4. The following results have been found:

- (A) To receive data more rapidly from the other flip-flop, the collector-to-substrate capacitance of transistor Q6, Q7 or the collector load resistance R11 must be reduced. The slope indicated by the arrow in Fig. 4 increases as these are reduced.

- (B) Additional capacitance CB in Fig. 1 synchronizes the current switch symmetrically with the input clock, as shown in Fig. 4 (without CB) and Fig. 5 (with CB).

The clock frequencies in Fig. 3, 4 and 5 are 2.5 GHz; half a pulse section is 200 pS. Horizontal time scales are 500 pS/division for Fig. 2, 1nS/division for Fig. 3 and 400 pS/division for Fig. 4, 5. Left voltage scale (1V/division) is for the voltage waveform node 26 to 29 and 32. Right voltage scale (5uV/division) is for the voltage waveform between node 23 and 230, or between node 24 and 240. These internodal waveforms show the current which flows through an imaginary 0.001 ohm resistor (ie. 5mA/division), and indicates current switch operation.

Fig. 1 Master-slave flip-flop circuit.

Fig.2 Simulated Waveform of Miscounting (3.4GHz).

Fig.3 Start of Counting Waveform (2.5GHz).

Fig. 4 Precise Waveform without CB (2.5GHz).

Fig. 5 Precise Waveform with CB (2.5GHz).

#### PROCESS DESIGN

Several Si monolithic bipolar IC processes have been reported, most notably SST-1A (3) and APSA (4). A Si microwave monolithic IC process without self-alignment method, has also been reported (5). This process is called DNP-I (Direct Nitride Passivated base surface -I) and is capable of producing a transistor with a cut-off frequency of 6.5 GHz.

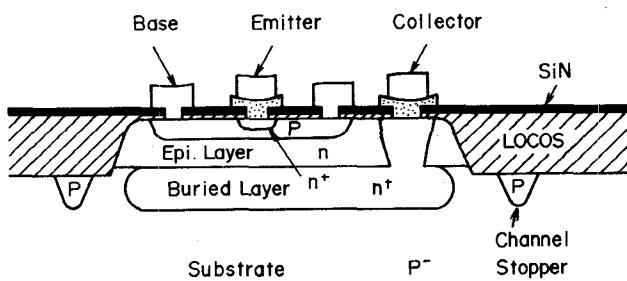

To achieve the transistor parameters determined by the computer simulation studies, the DNP-I process has been enhanced and is herein after referred to as a DNP-II process. This enhanced process has the following features:

- (A) To reduce parasitic capacitance, oxide isolation is applied, and a smaller buried layer is selected.

- (B) To achieve  $f_T = 10$  GHz, a shallow base ( $X_{jc}=0.2\mu m$ ) is formed by ion implantation and lamp-anealing. A shallow emitter ( $X_{je}=0.1\mu m$ ) is formed by diffusion from As-doped polysilicon.

- (C) To reduce base resistance and E-B junction capacitance, an emitter of 1  $\mu m$  width is formed.

- (D) To facilitate pattern design and form highly reliable electrodes, a Ti-Pt-Au electrode structure is employed.

- (E) To achieve an extremely high reliability, the base surface is covered by an additional nitride film after the thin oxide film is applied.

A cross sectional view of a DNP-II transistor cell is shown in Fig. 6. Table 1 compares the profiles produced by DNP-I and DNP-II processes. In the case of the DNP-II profile a great contraction in pattern rule was obtained and the base and collector regions are reduced to less than 60 %. Table 2 compares the performance of transistors produced by DNP-I and DNP-II processes.

#### RESULTS

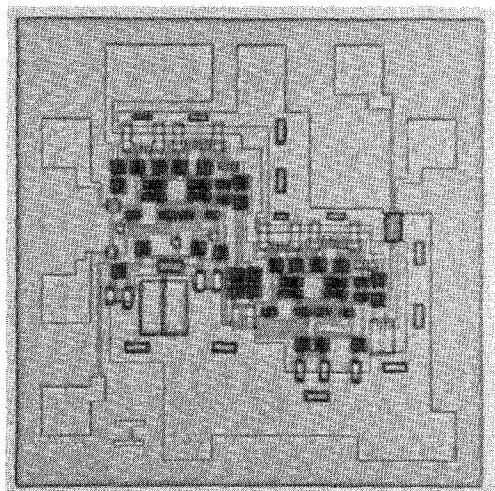

A die photograph is shown in Fig. 7 which includes the tandem two-stage master slave flip-flop from Fig. 1. Additional capacitor CB is composed of a buried layer and electrode; resistors are P+ polysilicon.

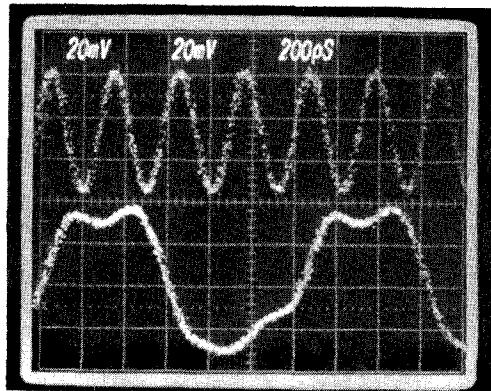

Operating waveforms at 3.3 GHz are shown in Fig. 8. The maximum operating frequency of 3.9 GHz has been achieved at a power dissipation of 316 mW and a supply voltage of 5 V.

#### CONCLUSION

A prescaler IC operating up to 3.9 GHz has been developed. This IC will be useful for the size reduction of microwave local oscillators.

This new IC process, based on the latest discrete microwave transistor process, is applicable to other microwave monolithic ICs.

#### ACKNOWLEDGMENTS

The authors wish to thank Mr. Kitagawa and Mr. Haga of NEC Corporation for their useful advice and encouragement. They also wish to thank Dr. Yanagawa for the CAD program.

Table 1. Basic Transistor Profile Comparison.

| item                | DNP-I                      | DNP-II                     |

|---------------------|----------------------------|----------------------------|

| Emitter width       | 1 $\mu$ m                  | 1 $\mu$ m                  |

| Emitter length      | 40 $\times$ 4 $\mu$ m      | 40 $\times$ 4 $\mu$ m      |

| Base area           | 290.4 $\mu$ m <sup>2</sup> | 159.6 $\mu$ m <sup>2</sup> |

| Collector area      | 496.8 $\mu$ m <sup>2</sup> | 288.0 $\mu$ m <sup>2</sup> |

| Electrode width     | 5 $\mu$ m                  | 2 $\mu$ m                  |

| Electrode interval  | 2.5 $\mu$ m                | 2 $\mu$ m                  |

| Epitaxial thickness | 1.5 $\mu$ m                | 1.5 $\mu$ m                |

Table 2. Transistor Performance Comparison.

| Parameter         | DNP-I  | DNP-II |

|-------------------|--------|--------|

| BV <sub>cbo</sub> | 25V    | 25V    |

| BV <sub>ceo</sub> | 12V    | 12V    |

| BV <sub>ebo</sub> | 4V     | 3V     |

| h <sub>FE</sub>   | 100    | 100    |

| f <sub>T</sub>    | 6.5GHz | 10GHz  |

Fig. 6 A cross sectional view of transistor cell.

Fig. 7 Die Photograph.

Fig. 8 Measured input output waveforms of an 1/4 divider for a 3.3 GHz sinusoidal clock.

#### REFERENCES

- (1) N.Kusama,et al." Tunable Phase-Locked Oscillator with Digital Frequency Divider",NEC Reseach & Development No. 53,pp.56-61,April 1979.

- (2) Y.Akazawa, et al." Low Power 1GHz Frequency Synthesizer LSI's", IEEE Trans. SC-18, No.1,pp.115-121,February 1983.

- (3) T.Sakai,et al."Gigabit Logic Bipolar Technology:Advanced Super Self-Aligned Process Technology", Electronic Letters Vol.19, No. 8,pp.283-284,April 1983.

- (4) H.Nakashiba,et al." An Advanced PSA Technology for High-Speed Bipolar LSI" IEEE Trans. ED-27, No.8, pp.1390- 1394 August 1980.

- (5) T.Nakata,et al." Si-Monolithic Micro-wave Wideband Amplifier",The Trans. of the IECE of Japan,Vol.E66, No. 8,pp.502- 503, August 1983.